# An FPGA Based Control Algorithm for Cascaded Multilevel Inverters

V.Kumar Chinnaiyan, Dr.Jovitha Jerome and J.Karpagam, Member IEEE

Abstract-In recent years, thanks to the various developments in VLSI, Field-Programmable Gate Arrays (FPGAs) have become key components in implementing high performance digital signal processing (DSP) systems, especially in the areas of digital communications, networking, video and imaging but its potential is not fully utilized in the area of power control and conversions. The logic fabric of today's FPGAs consists not only of look-up tables, registers, multiplexers, distributed and block memory, but also dedicated circuitry for fast adders, multipliers, and I/O processing (e.g., giga-bit I/O). The memory bandwidth of a modern FPGA far exceeds that of a microprocessor or DSP processor running at clock rates two to ten times that of the FPGA. Coupled with a capability for implementing highly parallel arithmetic architectures, this makes the FPGA ideally suited for creating high-performance custom data path processors for tasks such as digital filtering, fast Fourier transforms, and forward error correction.

In this paper a XILINX FPGA based multilevel PWM three phase inverter test rig was constructed by adding bi-directional switches to the conventional bridge topology and its performance is suitably analysed. The inverter can produce three and five different output voltage levels across the load. XILINX FPGA is a programmable logic device developed by XILINX which is considered as an efficient hardware for rapid prototyping. It is used as a SVPWM generator to apply the appropriate signals to inverter switches. In addition to XILINX FPGA, Matlab/Simulink, system Generator software was used for simulation and verification of the proposed circuit before implementation, Simulation and experimental results show that both are in close agreement. The present PWM signal generation scheme can be used for any multilevel inverter configuration with minimum changes in driver circuit.

*Keywords*— Cascaded Multilevel Inverter, FPGA, Space Vector Pulse Width Modulation, THD.

#### I. INTRODUCTION

MULTILEVEL converters offer many benefits for higher power applications. In particular, these include an ability to synthesise voltage waveforms with lower harmonic content than two level converters and operation at higher DC

This work is supported by SERC Division, Department of Science and Technology, Government of India

V.Kumar Chinnaiyan, is with the Department of Electrical and Electronics Engineering as Assistant Professor, Bannari Amman Institute of Technology, Coimbatore, India – 638 401 (Phone: +91 9942999111; fax: +914295223775;).

Dr. JovithaJerome, is with the Department of Instrumentation and Control Engineering as Professor and Head,PSG college of Technology, Coimbatore,India-641 014.

J.Karpagam, is with the Department of Electrical and Electronics Engineering as Assistant Professor, Bannari Amman Institute of Technology, Coimbatore, India –  $638\ 401$

voltages using series connected semiconductor switches. While many different multilevel converter topologies have been proposed, the two most common topologies are the Cascaded Inverter and its derivatives [1][2], and the Diode Clamped inverter [3]. Figure 1 shows topology for five level configuration of a Cascaded Multi Level Inverter. The two most popular control strategies for these multilevel inverter topologies are Carrier [4] and Space Vector (SVM)[6], [7] modulation.

An Field-Programmable Gate Array (FPGA), is a type of logic chip that can be programmed. An FPGA is similar to a PLD, but whereas PLDs are generally limited to hundreds of gates, FPGAs support thousands of gates. They are especially popular for prototyping integrated circuit designs. Once the design is set, hardwired chips are produced for faster performance. The inherent parallelism of the logic resources on an FPGA allows for considerable computational throughput even at a low MHz clock rates. The flexibility of the FPGA allows for even higher performance by trading off precision and range in the number format for an increased number of parallel arithmetic units. This has driven a new type of processing called reconfigurable computing, where time intensive tasks are offloaded from software to FPGAs [5].

SVM involves switching between the three nearest space vectors from the available states of an inverter. Several approaches have been presented to show how these space vectors can be selected for particular operating conditions [8]. For applications such as ac motor drives, it is desirable to minimize the harmonics and inter harmonics voltage to prevent premature bearing failure and reduce EMI levels. Several modulation variations that achieve this result have been reported SVM scheme.

The advantages of SVM [8]-[11] are as follows

- Line to line voltage amplitude can be as high as  $V_{DC}$ . Thus 100% VDC utilization is possible in the linear operating region.

- In the linear operating range, modulation index range is 0.0 to 1.0 in the sine PWM, where as in the SVM, it is 0 to 0.866. line to line voltage amplitude is 15% more in the SVM with the modulation index=0.866, compared to the SPWM with modulation Index = 1. Hence it has the better usage of the modulation index depth.

• With the increased output voltage, the user can design the motor control system with reduced current

rating, keeping the horse power rating at the same level. The reduced current helps to reduce the inherent conduction loss of the VSI.

• Only one reference space vector is controlled to generate the three phase sine waves.

• Implementation of SVM switching rules gives less THD and less switching loss.

• Flexibility to select inactive states and their distribution in switching time periods gives two degrees of freedom.

• As a reference space vector is a two dimensional quantity, it is feasible to implement more advanced vector control using SVM.

Figure 2 shows the space vector states for the proposed five level cascaded inverter.

Fig. 1 Five Level Cascaded Multilevel Inverter

Fig. 2 Space Vector States for 5 Level Inverter

# II. FPGA IMPLEMENTATION

The Field-Programmable Gate Arrays (FPGAs) have become key components in implementing high performance digital signal processing (DSP) systems [5]. The logic fabric of today's FPGAs consists not only of look-up tables, registers, multiplexers, distributed and block memory, but also dedicated circuitry for fast adders, multipliers, and I/O processing (e.g., giga-bit I/O). The memory bandwidth of a modern FPGA far exceeds that of a microprocessor or DSP

processor running at clock rates two to ten times that of the FPGA. Coupled with a capability for implementing highly parallel arithmetic architectures, this makes the FPGA ideally suited for creating high-performance custom data path processors for tasks such as digital filtering, fast Fourier transforms, and forward error correction. The processors and DSPs, even when running at GHz clock rates, are increasingly used for relatively low MIPs packet level processing, with the chip and symbol rate processing being implemented in the FPGAs and ASICs. The fluidity of emerging standards often makes FPGAs, which can be reprogrammed in the field, better suited than ASICs. Though VHDL provides many high level abstractions and language constructs for simulation, its synthesizable subset is far too restrictive for system design. System Generator is a software tool for modeling and designing FPGA-based DSP systems in Simulink. The tool presents a high level abstract view of a DSP system, yet nevertheless automatically maps the system to a faithful hardware implementation. The most significant is that System Generator provides these services without substantially compromising either the quality of the abstract view or the performance of the hardware implementation.

# A. System Generator

Simulink provides a powerful high level modeling environment for DSP systems, and consequently is idely used for algorithm development and verification. System Generator maintains an abstraction level very much in keeping with the traditional Simulink block sets, but at the same time automatically translates designs into hardware implementations that are faithful, synthesizable, and efficient [12]. The implementation is faithful in that the system model and hardware implementation are bit-identical and cycle-identical at ample times defined in Simulink. The implementation is made efficient through the instantiation of intellectual property (IP) blocks that provide a range of functionality from arithmetic operations to complex DSP functions [12]. These IP blocks have been carefully designed to run at high speed and to be area efficient. In System Generator, the capabilities of IP blocks have been extended transparently and automatically to fit gracefully into a system level framework. For example, although the underlying IP blocks operate on unsigned integers, System Generator allows signed and unsigned fixed point numbers to be used, including saturation arithmetic and rounding. User-defined IP blocks can be incorporated into a System Generator model as black boxes which will be embedded by the tool into the HDL implementation of the design.

## III. MODELING WITH SYSTEM GENERATOR

Before developing the hardware circuit for power, control and isolation circuit based on the FPGA, the entire system is generated with the aid of simulation package simulink/system generator for FPGA in order to verify the pulses and the patterns of the output pulses. The creation of a

DSP design begins with a mathematical description of the operations needed and concludes with a hardware realization of the algorithm [12]. The hardware implementation is rarely faithful to the original functional description instead it is faithful enough. The challenge is to make the hardware area and speed efficient while still producing acceptable results. In a typical design flow, a flow supported by System Generator the following steps occur:

1. Describe the algorithm in mathematical terms,

2. Realize the algorithm in the design environment, initially using double precision,

3. Trim double precision arithmetic down to fixed point,

4. Translate the design into efficient hardware.

Step 4 is error prone because it can be difficult to guarantee the hardware implements the design faithfully. System Generator eliminates this concern by automatically generating a faithful hardware implementation.

## IV. SIMULATION BLOCKS AND RESULTS

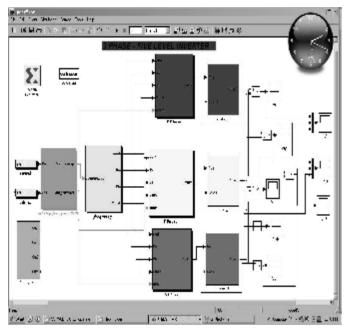

The proposed algorithm is generated in front end with the aid of system generator editor, the SVM blocks and the associated blocks for individual phases are inte4rconnected and the sampling frequency is set to 5kHz. The entire system is shown in figure 3.

Fig. 3 Block Diagram for Generation of firing pulses for Three Phase Five Level Cascaded Multilevel Inverter

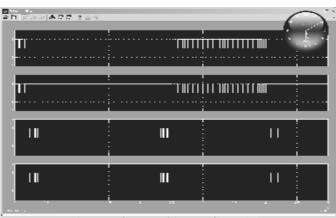

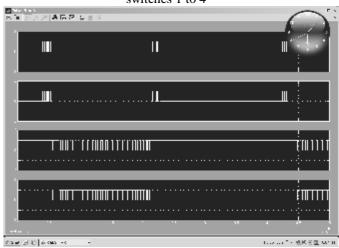

The generated output pulses from the main SVM blocks are converted in to eight numbers which is required to drive the devices in to ON state with the aid of pulse converter blocks as shown in figure 4. The pulse for the individual swithes from 1 to 4 is as shown in the figure 5 and the pulses for the switches from 5 to 8 is as shown in the figure 6, for the remaining switches these pulses are inverted suitably to the same group and supplied. The line to line and phase voltages are as shown in figure 7 and figure 8 respectively.

Fig. 5 Pulses for the Cascaded Multilevel Inverter switches 1 to 4

Fig. 6 Pulses for the Cascaded Multilevel Inverter switches 5 to 8

Figure 7 Output line to line voltages

Figure 8 output phase voltages

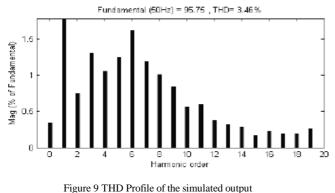

The switching patterns adopted are applied at the cascaded multilevel inverter switches to generate five or three output voltage levels at different modulation indexes. XILINX FPGA enables to make easy, fast and flexible design and implementation. The THD profile for the simulation system is as shown in the figure 9, which shows the results are well within the specified limits of IEEE standards. The experimental and simulated results are show satisfactory results in term of total harmonic distortion and output voltage and current waveform shapes

V. CONCLUSIONS

This paper proposes a FPGA based new PWM switching

strategy for the cascaded multilevel inverter (CMI). This scheme employs a Space Vector Modulation Technique. The main advantage of this technique is the ability to generate PWM waveform generation in real time using very simple algorithm in the XILINX processor. This reduces the cost for control circuit, computation time required to determine the switching times for inverter legs, memory requirement of the digital processors making the algorithm suitable for real-time implementation. Furthermore it also results in higher fundamental component magnitude. This paper carried out the simulation on a five level CMI to justify the merits of the proposed scheme. A low cost FPGA based three phase five-level CMI test-rig is also constructed to verify the simulation results.

#### ACKNOWLEDGMENT

The authors are very much grateful to the officials of the Department of Science and Technology for their financial support and their valuable suggestions, help at the critical times of this project. This research work is funded by the Department of Science and Technology, Government of India, New Delhi. Under the title of "Design Analysis and Experimentation of Low Cost DSP Based Multilevel Inverter for Industrial Applications with Reduced EMI and Other Power Quality Issues" Sanction order No.: SR/FTP/ETA-33/2006.

#### REFERENCES

- [1] R.S. Kanchan, M.R. Baiju, K.K. Mohapatra, P.P. Ouseph and K. Gopakumar, "Space Vector PWM Signal Generation for Multilevel Inverters Using only the Sampled Amplitudes of Reference Phase Voltages", IEE Proc. Electr. Power Appl., Vol 152, No.2, March 2005

- [2] Holtz, J.: 'Pulse Width Modulation–A Survey', IEEE Trans. Ind. Electron., 1992, 30, (5), pp. 410–420

- [3] Zhou, K., and Wang, D.: 'Relationship Between Space-Vector Modulation and Three-phase Carrier-based PWM: A Comprehensive Analysis', IEEE Trans. Ind. Electron., 2002, 49, (1), pp. 186–196

- [4] Van der Broeck, Skudelny, H.C., and Stanke, G.V.: 'Analysis and Realisation of a Pulse Width Modulator Based on Voltage Space Vectors', IEEE Trans. Ind. Appl., 1988, 24, (1), pp. 142–150

- [5] C. Cecati. M. Cirstea. M. Mc. Cormick-, P. Fioravanti, "Design of a FPGA Implementing a Passivity-based Pulsewidth Modulation', SPEEDAM 2002. 11-14 Giugno 2002. Ravello, Italia, pp. A2\_43-A2 48.

- [6] Boys, J.T., and Handley, P.G.: 'Harmonic Analysis of Space Vector Modulated PWM Waveforms', IEE Proc. Electr. Power Appl., 1990, 137, (4), pp. 197–204

- [7] Holmes, D.G.: 'The General Relationship between Regular Sampled Pulse Width Modulation and Space Vector Modulation for Hard Switched Converters'. Conf. Rec. IEEE Industry Applications Society (IAS) Annual Meeting, 1992, pp. 1002–1009

- [8] Lee, D., and Lee, G.: 'A Novel Overmodulation Technique for Space Vector PWM Inverters', IEEE Trans. Power Electron., 1998, 13, (6), pp. 1144–1151

- [9] Kim, J., and Sul, S.: 'A Novel Voltage Modulation Technique of the Space Vector PWM'. Proc. Int. Power Electronics Conf., Yokohama, Japan, 1995, pp. 742–747

- [10] Carrara, G., Gardella, S.G., Archesoni, M., Salutari, R., and Sciutto, G.: 'A new Multi-level PWM Method: A Theoretical Analysis', IEEE Trans. Power Electron., 1992, 7, (3), pp. 497–505

- [11] Baiju, M.R., Mohapatra, K.K., Somasekhar, V.T., Gopakumar, K., and Umanand, L.: 'A Five-level Inverter Voltage Space Phasor Generation for an Open-end Winding Induction Motor Drive', IEE Proc. Electr. Power Appl., 2003, 150, (5), pp. 531–538

- [12] XtremeDSP Starter Kit Spartan-3A DSP Application notes and product information available online at (<u>www.xilinx.com</u>)

ation Technology

#### IACSIT International Journal of Engineering and Technology Vol.1,No.5,December,2009 ISSN: 1793-8236

V.Kumar Chinnaiyan, He completed his M.E. in Power Electronics and Drives from PSG College of Technology, Coimbatore, India. He has the industrial experience of around three years. At present he is working as a Assistant Professor in EEE Department at Bannari Amman Institute of Technology, Sathyamangalam and he is in this profession since 2002. Till now he completed two consultancy projects. Currently he is working in another sponsored project funded by DST, New Delhi, in the domain of multilevel inverters which is also his research topic for his Ph.D. pursuing under Anna University, Chennai. His area of interest includes Power Quality, Harmonics, DSP solution for AC and DC Drives, Embedded systems. So far he published around twenty five papers in national level and International conferences.

**Dr. Jovitha Jerome**, She is working as Professor and Head, Instrumentation and Control Engineering at PSG College of Technology, Coimbatore, India. She has published more than

30 papers in National and International Journals. Her area of research includes Distribution Automation, Power System Management, Operation and Control, Virtual Instrumentation.

**J.Karpagam**, She completed her Masters degree in the specialization of Power Electronics and Drives from Anna University Chennai, India. Presently she is working as Assistant Professor in the department of Electrical and Electronics Engineering at Bannari Amman Institute of Technology Tamilnadu, India and she is in this profession

since 1999. Currently she is pursuing her Ph.D. in the area of multilevel converters applications to AC Drives under Anna University Coimbatore. Her area of interest Includes Power Electronics, DSP applications to Power Electronics and wind power generation, Solid State Drives, Power Converters, AC & DC drives. So far she has published around ten papers in national level and International conferences.